Ich mag Countdown-Timer und ich mag Logik-Bausteine. Daher erschien es ein naheliegendes Projekt zu sein einen Countdown-Timer aus Logik-Bausteinen aufzubauen. Ich habe mich für TTL-Bausteine aus der 74LS-Familie entschieden und war überrascht, wie umständlich das ganze ist.

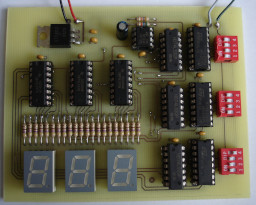

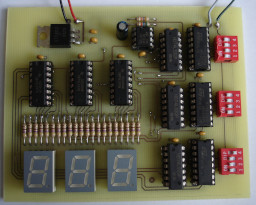

Im Folgenden habe ich das Board-Layout farblich gekennzeichnet und erkläre die einzelnen Bestandteile meiner Schaltung.

|

|

Die Spannungsversorgung (blau) wird von einem 7805 in Standard-Beschaltung (zwei kleine Kondensatoren gegen Rückkopplung/Schwingen) gebildet. Sie erzeugt aus einer Eingangsspannung von mindestens 7 Volt eine geglättete Gleichspannung von 5 Volt. Bei den Spannungsreglern der 78xx-Familie handelt es sich um Linearregler. Hier gilt zu beachten, dass die Differenz aus Eingangs- und Ausgangsspannung im wahrsten Sinne des Worte "verbraten" wird, d.h. vollständig in Wärme umgewandelt wird.

Jedes IC hat noch einen kleinen Kondensator mit 100 nF als direkten Nachbarn. Diese Kondensatoren sollen plötzliche Einbrüche in der Versorgungsspannung ausgleichen. Insbesondere sequenzielle Logik (z.B. Zähler) verhält sich mitunter ausgesprochen merkwürdig, wenn man auf diese kleinen Kondensatoren verzichtet.

Der Takt des Countdown-Timers wird von einem NE555 (grün) gebildet. Dieser erzeugt mit meiner Beschaltung eine fallende Flanke pro Sekunde, die als Takt in die Zähler eingespeist wird. Die Reset-Leitung des Taktgebers wird von der Null-Erkennung bedient um den Zähler bei "000" anzuhalten.

Der eigentliche Countdown entsteht in den orange markierten Zähler-Bausteinen vom Typ 74LS192. Dies sind BCD-Zähler, d.h. sie geben jeweils eine Ziffer von 0 bis 9 in Binärform aus. Sie werden beim Start des Timers über die benachbarten DIP-Switche (hellgrün) mit einem Wert vorbelegt. Untereinander sind sie über den "borrow"-Pin verbunden, das ist der Übertrag bei Subtraktionen. Fällt somit ein Zähler unter 0 wird der nächste Zähler ebenfalls um eins dekremntiert (z.B. um von "90" auf "89" zu gelangen).

Die Null-Erkennung (rot) verknüpft alle Zählerausgänge über logische ODER-Verknüpfungen miteinander. Hier werden 74LS32-Bausteine benutzt, die jeweils vier 2-Input-ODER-Gatter beinhalten. Wenn alle Eingaben auf LOW stehen ist der Gesamtwert ebenfalls LOW und führt zum Stoppen des Taktgebers. Weiterhin wird dieses Signal auch nach Außen bereitgestellt, falls man mit dem Timer tatsächlich irgendetwas steuern möchte.

Die drei Zählerstände werden von der Dekodier-Loigk (violett) auf die Anzeigemuster für die 7-Segment-Anzeigen abgebildet. Dies für sich genommen wäre schon eine gigantische Logik-Schaltung, aber zum Glück gibt es für diesen häufigen Anwendungsfall den 74LS47.

In meiner Schaltung kommen drei dieser ICs zum Einsatz und steuern über insgesamt 21 Widerstände die drei 7-Segment-Anzeigen an. Ein anderer Weg dies zu tun wird von meinem TTL-Counter mit Multiplex-Anzeige beschritten.

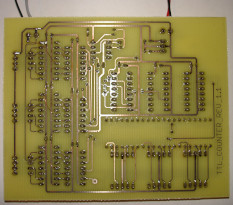

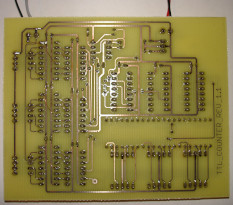

Die Leiterplatte habe ich selbst hergestellt. Man sieht einige geflickte Leiterbahnen und wenn man genau hinsieht den Versatz zwischen Ober- und Unterseite (an den Vias). Außerdem hatte ich mich bei der Bestückung für die Verwendung von 74HC-Bausteinen entschieden, was ein paar weitere kleine Anpassungen mit sich gebracht hat.

Bei 74LS-Bausteinen haben unbeschaltete Eingänge einen definierten Zustand (HIGH). Für Bausteine der 74HC-Serie gilt dies nicht, diese floaten undefiniert umher und fangen dabei jede noch so kleine Störung ein. In meinem Fall musste ich die "UP"-Eingänge der Zähler mittels Kupferlackdraht auf VCC ziehen, weil der Zähler sonst sporadisch aufwärts gezählt hat.

Weiterhin habe ich zwei SMD-Widerstände eingefügt, die den "CLR"-Eingang nach GND und den "LD"-Eingang nach VCC ziehen. Diese Leitungen sollen vom Benutzer der Schaltung bedient werden (Timer-Reset und Übernahme des voreingestellten Werts). Wenn sie aber nicht von einem anderen Schaltungsteil auf einen definierten Wert gehalten werden gibt es auch hier zufälliges Verhalten.

| Version | Datum | Änderungen | Datei | Beschreibung |

|---|---|---|---|---|

| 1.1 | 2007-03-25 | Erstes Release | TTL-Counter.zip | Schaltplan und Layout im Eagle-Format (konvertiert auf Version 9.2) |